## Modeling Custom Hardware in VHDL

Technical Report ICS-99-29 July 6, 1999

Heiko Lehr

Supervised by Prof. Daniel D. Gajski

Research Paper "Studienarbeit"

Department of Information and Computer Science University of California, Irvine Irvine, CA 92697-3425, USA (949) 824-8059

#### Abstract

This report focuses on models for describing Hardware at different refinement levels within High Level Synthesis flow: SFSMD, FSMD and FSM Controlling Datapath. Simple data interfaces are often needed in these models. The hardware description language VHDL is used and tested for implementing these models and interfaces. Problems inherent in the models as well as problems caused by VHDL are discussed. A model related main difficulty is the one-cycle delay of data processing, when introducing a datapath. VHDL descriptions of abstract models (SFSMD) can become complicated. Templates for general problems, examples and VHDL guidelines are provided in this report to help to minimize design errors significantly.

# Contents

| 1 |      | meaning of the models                                | 1   |

|---|------|------------------------------------------------------|-----|

|   | 1.1  | SFSMD                                                | ]   |

|   |      | 1.1.1 Behavioral Description                         | 2   |

|   |      | 1.1.2 Structural Description                         | 2   |

|   | 1.2  | FSMD                                                 | 2   |

|   |      | 1                                                    | 3   |

|   |      |                                                      |     |

|   | 1.3  | 0 1                                                  | 9   |

|   |      | 1.3.1 Behavioral Description                         | 4   |

|   |      | 1.3.2 Behavioral-Structural Description              | 4   |

|   |      | 1.3.3 Structural Description                         | 5   |

|   | 1.4  | FSM                                                  | 5   |

|   | 1.5  | Conclusion                                           | 5   |

| 2 | Sch  | duling, Allocation and Binding                       | 6   |

| 3 | VHI  | OL Programming Structure                             | e   |

|   |      |                                                      |     |

| 4 |      | ribing the Models in VHDL                            | 8   |

|   | 4.1  | Abstract and Introduction                            | 8   |

|   |      | 4.1.1 The State Machines Graphically                 | 8   |

|   |      | 4.1.2 Translation into VHDL                          | 8   |

|   | 4.2  | Examples and Guidelines                              |     |

|   |      | 4.2.1 SFSMD Behavioral                               |     |

|   |      | 4.2.2 FSMD Behavioral                                | 2   |

|   |      | 4.2.3 Discussion: FSMD Behavioral                    |     |

|   |      | without time or with clock                           | 3   |

|   |      | 4.2.4 FSM Behavioral Controlling Datapath Structural | 4   |

|   |      | 4.2.5 FSM Structural Controlling Datapath Structural | 4   |

|   |      | 4.2.6 Compensation of Datapath Delay                 | 4   |

| 5 | Con  | munication                                           |     |

|   | of S | rate Machines 2                                      | 5   |

|   | 5.1  | Single Handshake                                     | 5   |

|   | 5.2  | Double Handshake                                     |     |

|   | 5.3  | Examples:                                            |     |

|   |      | Data-Transfer Constructions in VHDL                  | 2   |

|   |      | 5.3.1 Direct Data-Transfer                           |     |

|   |      | 5.3.2 Data-Transfer via Queue                        |     |

|   |      | 5.3.3 Data-Transfer via Memory                       |     |

| 6 | Des  | ribing the Models in VHDL                            |     |

| Ŭ |      | mmary of Problems                                    |     |

|   |      | Conclusions 4                                        | Δ   |

|   | 6.1  | Single Models in VHDL                                |     |

|   | U.1  | 6.1.1 SFSMD and FSMD Without Time                    |     |

|   |      | 6.1.2 FSMD With Clock                                |     |

|   |      |                                                      |     |

|   | 6.9  | 0 1                                                  |     |

|   | 6.2  | Communicating Models in VHDL                         |     |

|   |      | 6.2.1 SFSMD and FSMD Without Time                    |     |

|   |      | 6.2.2 FSMD With Clock                                | . 0 |

|              | $\begin{array}{c} 6.3 \\ 6.4 \end{array}$ |                             | Controlling Datapath                                                                              |     |

|--------------|-------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------|-----|

| Re           | efere                                     | $_{ m nces}$                |                                                                                                   | 46  |

| A            | Qu€                                       | eue wit                     | h Single Handshake                                                                                | 47  |

|              | <b>A</b> .1                               | FSMD                        |                                                                                                   | 47  |

|              | A.2                                       | FSM f                       | or "FSM Controlling Datapath"                                                                     | 48  |

| В            |                                           |                             | v                                                                                                 | 49  |

|              | B.1                                       | FSM f                       | or Queue with Simultaneous Read/Write                                                             | 49  |

|              | B.2                                       | Extend                      | led Timing for Memory                                                                             | 50  |

| $\mathbf{C}$ | VH                                        | DL exa                      | amples                                                                                            | 51  |

|              | C.1                                       |                             | Finite State Machines                                                                             | 51  |

|              |                                           | C.1.1                       | Single SFSMD                                                                                      |     |

|              |                                           | C.1.2                       | Single FSMD without time                                                                          | 54  |

|              |                                           | C.1.3                       | Single FSMD using clock                                                                           |     |

|              |                                           | C.1.4                       | Single FSM Controlling Datapath                                                                   | 58  |

|              |                                           | $\overline{\mathrm{C.1.5}}$ | 9 -                                                                                               |     |

|              |                                           | C.1.6                       |                                                                                                   |     |

|              | C.2                                       | Double                      | e Handshake                                                                                       | 64  |

|              |                                           | C.2.1                       |                                                                                                   |     |

|              |                                           |                             |                                                                                                   |     |

|              |                                           |                             |                                                                                                   |     |

|              |                                           | C.2.4                       | A (FSMD using clock) $\rightarrow$ B (FSMD using clock)                                           |     |

|              |                                           | _                           | FSMD A                                                                                            |     |

|              |                                           | C.2.6                       | FSMD B                                                                                            |     |

|              |                                           | C.2.7                       | A (FSM Controlling Datapath) → B (FSM Controlling Datapath)                                       |     |

|              |                                           | C.2.8                       | FSM Controlling Datapath A                                                                        |     |

|              |                                           | C.2.9                       | FSM of A                                                                                          |     |

|              |                                           | C.2.10                      | Datapath of A (identical B)                                                                       |     |

|              |                                           |                             | FSM Controlling Datapath B                                                                        |     |

|              |                                           |                             | FSM of B                                                                                          |     |

|              |                                           |                             | Datapath of B                                                                                     |     |

|              | C.3                                       |                             | er via Queue with Double Handshake                                                                |     |

|              |                                           |                             | A (FSMD without time) $\rightarrow$ Queue (FSMD without time) $\rightarrow$ B (FSMD without time) |     |

|              |                                           |                             | FSMD A                                                                                            |     |

|              |                                           | C.3.3                       | FSMD Queue                                                                                        |     |

|              |                                           | C.3.4                       | FSMD B                                                                                            |     |

|              |                                           | C.3.5                       | A (FSMD using clock) $\rightarrow$ Queue (FSMD using clock) $\rightarrow$ B (FSMD using clock)    |     |

|              |                                           | C.3.6                       | FSMD A                                                                                            |     |

|              |                                           | C.3.7                       | FSMD Queue                                                                                        |     |

|              |                                           | C.3.8                       | FSMD B                                                                                            |     |

|              |                                           | C.3.9                       | A (FSM Controlling Datapath) → Queue (FSM Controlling Datapath)                                   |     |

|              |                                           | 0.0.0                       | → B (FSM Controlling Datapath)                                                                    | 110 |

|              |                                           | C.3 10                      | FSM Controlling Datapath A                                                                        |     |

|              |                                           |                             | FSM of A                                                                                          |     |

|              |                                           |                             | Datapath of A (identical B)                                                                       |     |

|              |                                           |                             | FSM Controlling Datapath Queue                                                                    |     |

|              |                                           |                             | FSM of Queue                                                                                      |     |

|              |                                           |                             | Datapath of Queue (Buffered)                                                                      |     |

|              |                                           |                             | Datapath of Unbuffered Queue                                                                      |     |

|     | C.3.17 FSM Controlling Datapath B                            | 127 |

|-----|--------------------------------------------------------------|-----|

|     | C.3.18 FSM of B                                              | 129 |

|     | C.3.19 Datapath of B identical to A (see A)                  | 132 |

| C.4 | Transfer via Memory with Double Handshake                    | 133 |

|     | C.4.1 A (FSM Controlling Datapath) → Memory    Arbiter (FSM) |     |

|     | → B (FSM Controlling Datapath)                               | 134 |

|     | C.4.2 FSM Controlling Datapath A                             | 136 |

|     | C.4.3 FSM of A                                               | 138 |

|     | C.4.4 Datapath of A (identical B)                            | 142 |

|     | C.4.5 Memory                                                 | 144 |

|     | C.4.6 Arbiter (FSM)                                          | 145 |

|     | C.4.7 FSM Controlling Datapath B                             | 147 |

|     | C.4.8 FSM of B                                               | 149 |

|     | C.4.9 Datapath of B identical to A (see A)                   | 154 |

# List of Figures

| 1  | Models for HL-Synthesis                                                               |

|----|---------------------------------------------------------------------------------------|

| 2  | System Exploration Chart                                                              |

| 3  | One-State-SFSMD                                                                       |

| 4  | SFSMD                                                                                 |

| 5  | FSMD Behavioral                                                                       |

| 6  | FSM Controlling Datapath (1)                                                          |

| 7  | Multi purpose datapath                                                                |

| 8  | FSM Controlling Datapath (2)                                                          |

| 9  | General VHDL program structure                                                        |

| 10 | A state machine inside a procedure                                                    |

| 11 | A state machine inside a process                                                      |

| 12 | A state machine for controlling a separate datapath                                   |

| 13 | Example: SFSMD Behavioral in VHDL                                                     |

| 14 | Example: FSMD Behavioral Without Time in VHDL                                         |

| 15 | Example: FSMD Behavioral With Clock in VHDL                                           |

| 16 | Example: Datapath of "FSM Behavioral Controlling Datapath Structural"                 |

| 17 | Example: FSM of "FSM Behavioral Controlling Datapath Structural"                      |

| 18 | Example: FSM of "FSM Structural Controlling Datapath Structural"                      |

| 19 | Warning: Omitting separation of next-state-process causes additional output latches   |

| 20 | Embedding the example SFSMD (fig. 13) in VHDL                                         |

| 21 | Embedding the example FSMD Without Time (fig. 14) in VHDL                             |

| 22 | Embedding the example FSMD With Clock (fig. 15) in VHDL                               |

| 23 | Embedding the example "FSM Controlling Datapath" (fig. 16 and 17) in VHDL             |

| 24 | Single Handshake                                                                      |

| 25 | Cases, when using Single Handshake with two FSMD                                      |

| 26 | Cases, when using Single Handshake with two FSM                                       |

| 27 | Cases, when using Single Handshake with a FSM transmitting to a FSMD                  |

| 28 | Cases, when using Single Handshake with a FSMD transmitting to a FSM                  |

| 29 | Insertion of a "General State" in the receiving state machine of figure 30            |

| 30 | Double Handshake                                                                      |

| 31 | Timing problem when writing                                                           |

| 32 | Timing problems when receiving                                                        |

| 33 | Direct data-transfer with Double Handshake: Block structure for FSMDs                 |

| 34 | Direct data-transfer with Double Handshake: Refinement to FSMs and datapaths          |

| 35 | Data-transfer via queue with Double Handshake: Block structure for FSMDs              |

| 36 | Data-transfer via queue with Double Handshake: FSMDs                                  |

| 37 | Data-transfer via queue with Double Handshake: Refinement to FSMs and Datapaths       |

| 38 | Datapath of buffered queue                                                            |

| 39 | Data-transfer via queue with Double Handshake: FSMs                                   |

| 40 | Data-transfer via memory with Double Handshake: Structure                             |

| 41 | Data-transfer via memory with Double Handshake: FSMs                                  |

| 42 | Statemachines for Single Handshake via Queue (FSMD)                                   |

| 43 | Statemachines for Single Handshake via Queue (FSM Controlling Datapath)               |

| 44 | Statemachines for Doublehandshake via Queue with simultaneous Read/Write              |

| 45 | Statemachines with Extended Timing Properties for Doublehandshake via Memory (FSM) 50 |

### Modeling Custom Hardware in VHDL

#### Heiko Lehr

#### Abstract

This report focuses on models for describing Hardware at different refinement levels within High Level Synthesis flow: SFSMD, FSMD and FSM Controlling Datapath. Simple data interfaces are often needed in these models. The hardware description language VHDL is used and tested for implementing these models and interfaces. Problems inherent in the models as well as problems caused by VHDL are discussed. A model related main difficulty is the one-cycle delay of data processing, when introducing a datapath. VHDL descriptions of abstract models (SFSMD) can become complicated. Templates for general problems, examples and VHDL guidelines are provided in this report to help to minimize design errors significantly.

### 1 The meaning of the models

In order to discuss High Level Synthesis, different specification models are important.

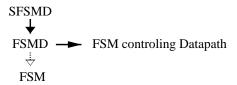

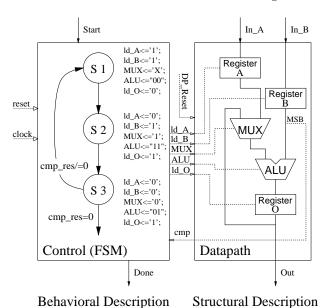

Figure 1: Models for HL-Synthesis

Figure 1 shows the refinement flow of the models. The models used for high level synthesis are connected by the solid arrows. The FSMD to FSM flow is not useful (indicated by a dotted arrow). The horizontal arrow indicates, that the connected models are on the same refinement level. They are related strongly, but their ideas and possibilities for usage are differently.

Theoretically, each model could be described behaviorally and structurally. However depending on the model, such a description may be impractical or even meaningless because of an exploding size or complexity of the description.

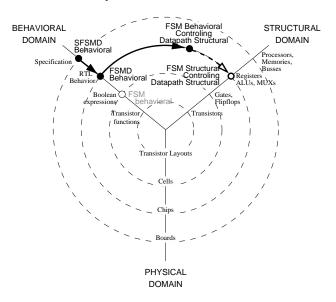

Figure 2 shows the system exploration chart (Y-Chart). It consists of refinement levels (circles) and description domains (lines). The significant description models are marked in the chart.

The following sections explain these models. Additionally, description models of little or no use are mentioned briefly.

Figure 2: System Exploration Chart

#### 1.1 SFSMD

The Super Finite State Machine with Datapath (SF-SMD) is the most abstract level of description.

The whole algorithm can be considered to be a SF-SMD with one superstate. But generally, the algorithm can be divided into any number of parts of any size. These parts are the superstates.

The algorithm parts consist of reading inputs (I), writing outputs (O) and executing expressions (EXP), which use intermediate storage variables (V). Using these elements, SFSMD can be described syntactically in the same way as FSMD. (See FSMD below.) The

basic difference between the two models is, that SF-SMD does not restrict the size of the algorithm-parts assigned to a state, whereas FSMD does. This is, because SFSMD does not correspond to hardware at all, whereas the states of FSMD correspond to clock cycles.

#### 1.1.1 Behavioral Description

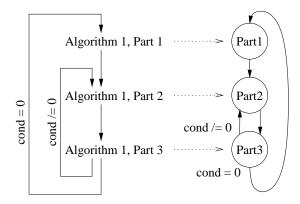

For behavioral description, the algorithm which is chosen to be implemented in hardware must be correct and executable on any platform, but no restrictions concerning a special structure apply. The whole algorithm could be assigned to one single big superstate (figure 3). But in most cases several superstates are recommended. When describing the algorithm in a high level programming language, it is typical to map the procedures to superstates.

Figure 4 shows an example with several superstates. Like in every state machine, in SFSMD a superstate can have several possible successors. The valid one is determined by transition conditions as shown in state  $Part\ \mathcal{J}$  of the figure. The left-hand side "cond" can be a variable, but it also could be a function.

Figure 3: One-State-SFSMD

Figure 4: SFSMD

#### 1.1.2 Structural Description

A structural description is not used for this model. Hardware allocation and scheduling are not done at this point (see section 2). Therefore a structural description just could be something like a general purpose computer which is capable of executing the appropriate program which is stored in some memory (Y-Chart, fig. 2: structural domain, outer circle). This is not helpful for implementing a specialized algorithm.

#### 1.2 FSMD

In the model Finite State Machine with Datapath (FSMD) scheduling is performed (see section 2). That means, algorithm is divided into small pieces which are assigned to cycles using cycle based states. FSMD-cycles will be mapped to the cycles of the hardware clock. However hardware cycle time is not finally set yet. There may also be a multiplication factor in this mapping (e.g. each FSMD cycle lasts two clock cycles).

In each state two things are done:

- The operation scheduled to this state is executed within one clock cycle.

- The next state for the next clock cycle is determined.

For an exact description of FSMD, some sets have to be defined:

```

S: set of states I: set of inputs

```

V: set of storage variables

O: set of outputs EXP: set of expressions:

functions which give results depending on storage variables V and operators OP:

$EXP = \{V, OP\} = \{f(x, y, z, \ldots) | x, y, z \in V\}$

OP: set of operators used in EXP

STAT: set of status expressions:

logic relations between

two expressions from the set EXP:  $STAT = \{Rel(a,b)|a,b \in EXP\}$

Referring to the above definitions, the data processing (first item in above list) is described by function h:

$$h: S \times (I \cup STAT \cup EXP) \rightarrow (V \cup O); \qquad V0, S0$$

There needs to be a set of initializing values V0 for the variables V when starting the FSMD, because the expressions in EXP read them. There also has to be

an initial value S0 for the state.

The next state (item 2 in above list) is determined in a similar way:

$$f: S \times (I \cup STAT) \rightarrow S;$$

$V0, S0$

V0 and S0 are needed again, because STAT depends on EXP, and EXP depends on V.

With these definitions, a FSMD is described by:

$$\langle S, S0, (I \cup STAT \cup OP), V, V0, O, h, f \rangle$$

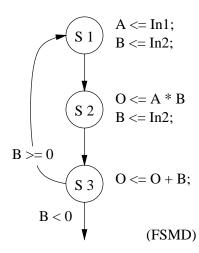

#### 1.2.1 Behavioral Description

The FSMD Behavioral description is shown in figure 5. Behavioral description is preferred for this model, because of better readability. It clearly illustrates how the code pieces are scheduled in the states. It is located at the RTL Behavior point of the Y-Chart. The term "RTL" (Register Transfer Level) indicates the cycle accuracy of this description and the corresponding register transfers of the final hardware:

Each variable used in this description will be assigned to elements of the final hardware (register, memory, input, output, delay-wire). Several variables may be assigned to the same element as long as their lifetimes do not overlap. However, the assignment itself is not done in this description. It is just assumed that each variable will have a location somewhere in the final hardware.

Figure 5: FSMD Behavioral

#### 1.2.2 Structural Description

A structural description is not used for this model. The structural description would look like figure 6, except that control and datapath are not separated into distinct blocks.

The following model is more suitable for a structural description.

#### 1.3 FSM Controlling Datapath

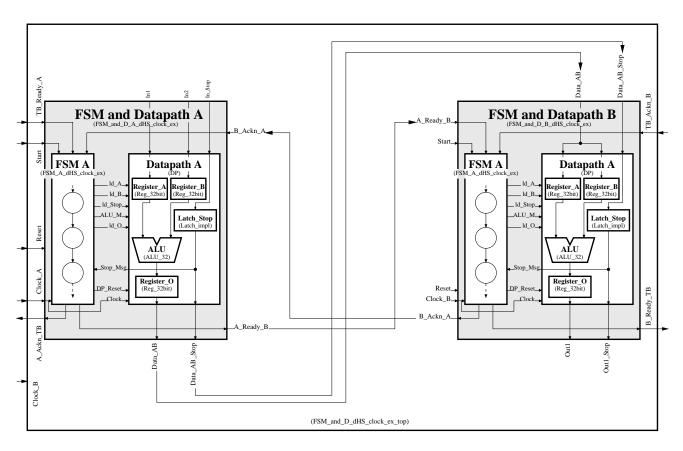

Here, the hardware is described on the same refinement level as the previous model. In contrast to FSMD, there is splitting into a *control*-part, described by a *Finite State Machine (FSM)* without datapath, and a separate datapath now.

The control block controls the execution of the operations while the datapath actually performs them. That means, compared to FSMD, the computation of the expression STAT and EXP are done in the datapath. Storage variables V, inputs I and outputs O are also covered by the datapath.

For the control block, the set of states S remains. Additionally, there are connections between control block and datapath:

C: Control signals (output of control FSM)

M: Message signals (input of control FSM)

The functions for the datapath look similar to the FSMD model. The difference is, that message and control signals are used instead of the state:

$$h_M: C \times (I \cup STAT \cup EXP) \to (V \cup O); \qquad V0, C0$$

$f_M: C \times (I \cup STAT) \to M; \qquad V0, C0$

$$< C, C0, (I \cup STAT \cup OP), V, V0, O, h_M, f_M >$$

The control block defines the relationships among message signals M, control signals C and states S:

$$h_C: S \times M \to C$$

$f_C: S \times M \to S$

$\langle S, M, C, h_C, f_C \rangle$

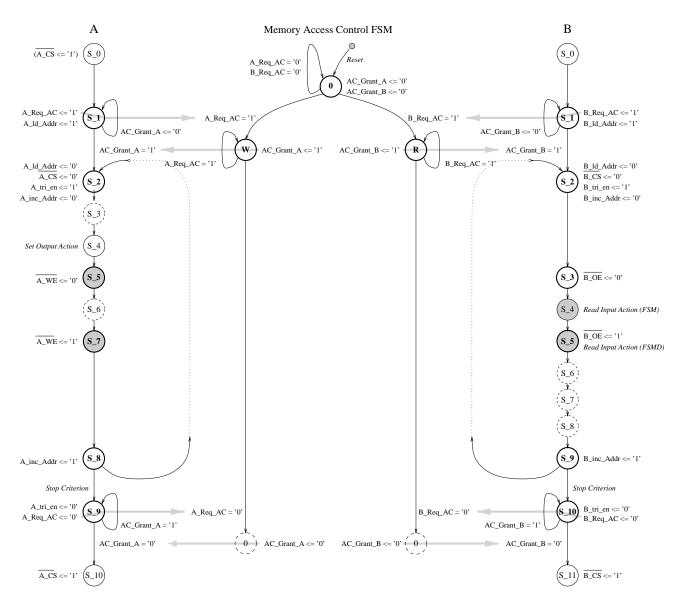

Depending on the current state, the control block sets control signals for the datapath. These signals tell the datapath which data are to be processed and how they are to be processed. The datapath can inform the control block about special results via message signals. See figures 6 and 8. Depending on the message signals, the control block determines the next state which becomes valid in the next clock cycle.

The separation into these two blocks offers new possibilities: Each can be independently described behaviorally or structurally.

#### 1.3.1 Behavioral Description

A pure behavioral description of this model is not used. When trying to describe this, there would be a second state machine for the datapath. This would cause lot of trouble:

If NC is the number of control signals from the control block to the datapath, then  $T = 2^{NC}$  is the number of different conditions for state transitions, which is an "exploding" expression.

Conclusion: A behavioral description of a separate datapath is not suitable. The model FSMD is used instead.

#### 1.3.2 Behavioral-Structural Description

The big advantage of the split model is the possibility of still using a behavioral description for the control, while describing the datapath structurally. See figure 6. The first block illustrates the states in accordance with the Register Transfer Level while the second contains the data structure: memory, registers, ALU and so on, as well as their connections and data inputand output ports. For example, a multiplication is implemented by the ALU and the result is stored in its output register. The ALU consists of pure combinational logic. The command signals from the FSM control the datapath: ALU = "11" chooses multiplication and 1d\_0 = '1' stores the result in register O.

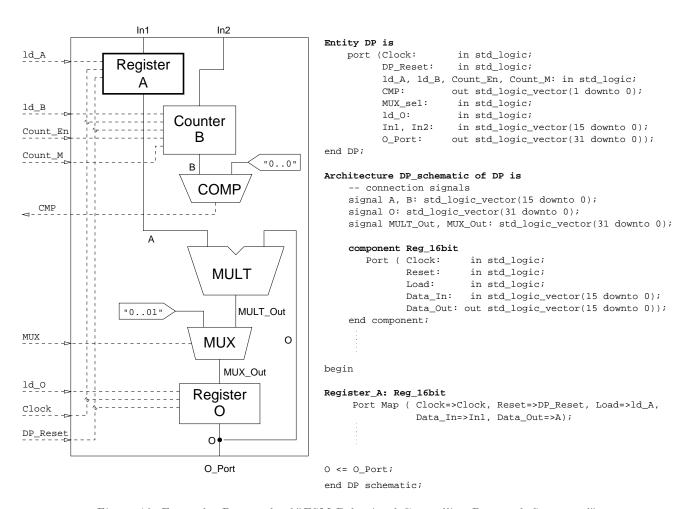

Figure 6: FSM Controlling Datapath (1)

Figure 7: Multi purpose datapath

This structural representation also illustrates the possible data flows. In figure 6, variables A and B can be multiplied by the ALU and the result can be stored in variable O which resides in register O.

Instead of the very specific datapath in figure 6, also a more general datapath can be used, like the one in figure 7. A general datapath often avoids the necessity of creating or changing the datapath when the control FSM is replaced or changed. On the other hand, a general datapath is less optimized and may contain unused overhead.

The huge amount of combinational logic is represented well in a datapath picture. For example, multiplier and comparator are purely combinational. That means, they do not use the clock and they do not contain any latches.

This pure structural description grows just linearly when inserting additional components. The size of a behavioral datapath description would have exploded. There would also be complicated transition conditions due to the huge amount of combinational logic.

In the control block, the situation is different: There are no "control data" which are modified and then passed to other operations. There is exactly one variable and it has special meaning: the state variable. It needs to be written and to be read. As its value is the basis for cycle accurate control, it has to be defined by a FSM in each clock cycle. For pointing out the state transitions and the state based interaction with the datapath, the behavioral description on the left-hand side in figure 6 is the best representation.

It is to say, that the split model with the control part described behaviorally and the datapath described structurally is more difficult to read by humans than a behavioral description of the model FSMD. However, this approach to the final hardware has to be taken. Physical hardware finally is obtained by implementing a structural description. Therefore we finally need a pure structural description. The datapath, which is by far the largest part of the design, is structural already. The behavioral control description is simple and can be converted to a structural description by a simple tool.

Conclusion: The split model with behavioral control and structural datapath is a good basis for synthesis tools which have some intelligence about how to convert behavioral description into structure. The model is still readable by humans.

#### 1.3.3 Structural Description

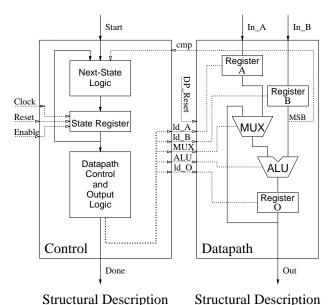

Synthesis tools with no intelligence may need a pure structural description. In figure 8, even the control part is structural. The control block shown here, implements the control FSM, too. However it reveals neither the states nor the associated actions any longer but hides them within the logic blocks. Even looking at the internal description of the logic blocks, pure structure is quite less readable.

Figure 8: FSM Controlling Datapath (2)

Conclusion: A pure structural description should be used only if the synthesis tool or the input language does not permit a behavioral description of the

control block.

#### 1.4 FSM

A Finite State Machine (FSM) without Datapath for describing the whole design (and not just the control) causes an explosion of the number of states:

Using no datapath means that for all possible data a separate state is needed. For example, a 16-bit integer variable causes 65536 different states. This has to be done for all other variables, too. As there is no datapath, a formal description of this model is simple. There are no storage variables and expressions using them. The only value which is stored is the state.

The functions for the next state and output are simplified to:

$$h: S \times I \to O$$

$$f: S \times I \to S$$

The FSM defining tuple is:

It is obvious, that the model FSM can only be used for problems which are dominated by boolean variables. They should not use variables which are larger than about 3 or 4 bits. Thus, this model is only suited for control algorithms, which are a special case. The FSM within the model "FSM Controlling Datapath" is an example.

However, for the general case, which includes data processing, this model can not be used reasonably.

Note: Synthesis tools may use this model for a hidden, automatically generated intermediate format in order to further refine the synthesis flow. But this is only necessary if low-level IPs (Intellectual Properties) like adder, multiplier and so on can not be provided as plug-ins for the datapath (see previous model).

#### 1.5 Conclusion

The above discussion points out the following models and descriptions. They are the best in most cases for performing High Level Synthesis with machine-human interaction.

#### 1. SFSMD Behavioral

(a) One-state SFSMD (general mathematical description or program)

- (b) Multi-state SFSMD (problem separation, structured program)

- 2. FSMD Behavioral

- 3. FSM Behavioral Controlling Datapath Structural

- 4. (FSM Structural Controlling Datapath Structural, if needed)

## 2 Scheduling, Allocation and Binding

The assignment of code slices to states is called *scheduling*. A slice of code from a FSMD Behavioral description should be as small to be executable within one cycle.

Exceptions can be made for some complex computations which cannot meet this constraint. They can also use multiple states.

Parallel execution of several incremental code pieces within one clock cycle can reduce the number of needed cycles and thus speed up the design. However there are two problems: One problem are the data dependencies. The simplest example is the impossibility of computing two values in parallel, if one is needed as an input for computing the other one. Another constraint is, that the datapath should not get too large exceeding restrictions in size or cost. For example, parallelizing two multiplications causes two multipliers in the datapath which significantly increases complexity.

So, when scheduling is performed for the behavioral description of the FSMD model, the *allocation* of data and actions partially should be planed already. It is accomplished in the structural description of the datapath however. The control block for the datapath points out the real requirements in a much more obvious way. The datapath has to be equipped with appropriate registers, memory and so on. This is the real execution of allocation.

Thereafter, binding has to be performed. The control block is adjusted to assign data to the right registers, correct memory addresses and other components.

### 3 VHDL Programming Structure

Generally, the "programming" language VHDL can be used for all the models and descriptions: Behavioral description of SFSMD, FSMD and for the description of a behavioral FSM controlling a structural datapath.

This section is a summary about the structure of VHDL programs. Those, who know VHDL well, may skip this section and proceed with section 4. For others, it helps to remember the structure of VHDL programs and to understand the following sections and examples better. However, this section does not teach VHDL.

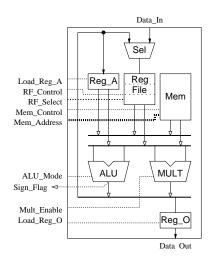

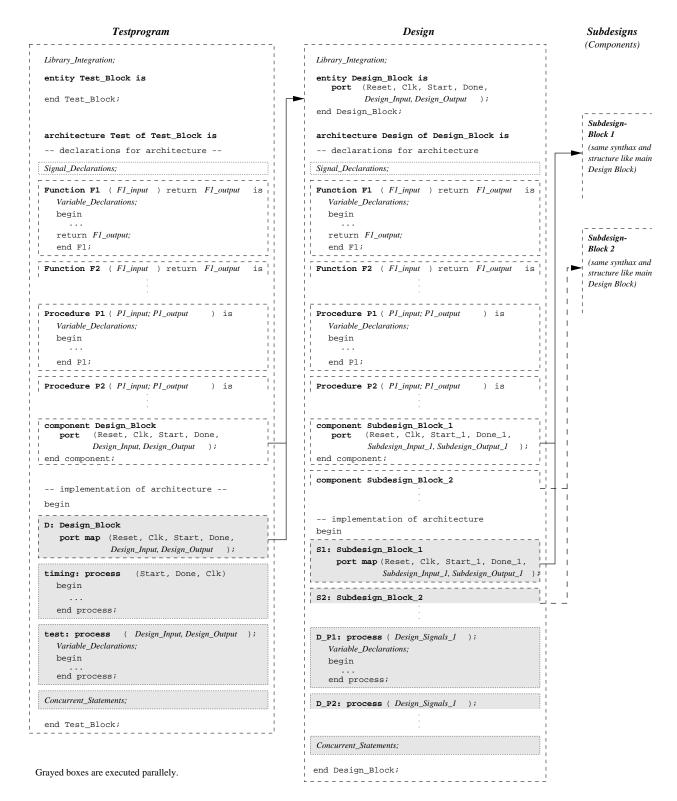

Figure 9 shows a simple general template for the structure of VHDL-code from which the description of the models will be derived. Some optional parts are omitted, because they are seldom used and not needed here

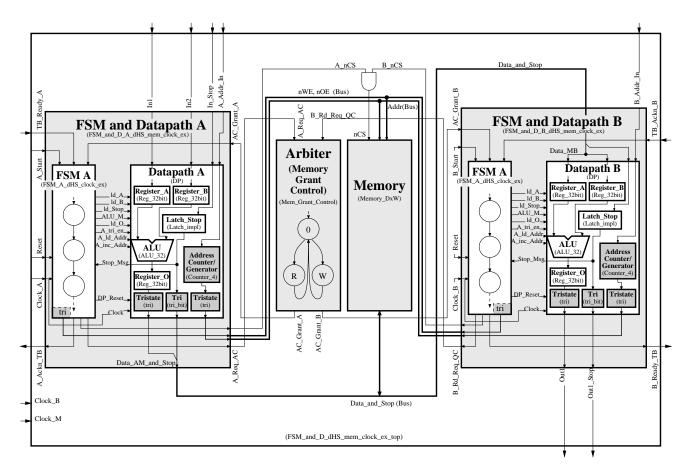

VHDL is block-oriented and in that way uses hierarchy. The hierarchy structure usually looks like the one shown in figure 7: A testbench forms the top level. It instantiates the design block which may have several subblocks. Subblocks can have subblocks themselves.

Except the testbench, the other blocks need to have data ports. The ports of the top level design block implement the inputs and outputs of the algorithm. The are independent of the currently used model and description. Therefore VHDL separates them: The entity covers the port declarations whereas the architecture implements the computation part.

The figure shows that the architecture consists of a declaration part and an implementation part. The latter one contains processes, subblock-instantiations and concurrent statements. They are executed parallelly, indicated by grayed boxes in the figure 9. Simple concurrent statements usually are a simple logic block. Processes behave like infinite loops of code. They temporarily have to be suspended before each run of the loop. This can be done by wait commands or by a so-called sensitivity list. Figure 9 uses sensitivity lists in the process heads, causing the process to wait on a change of the listed signals.

Subblock-components, functions, procedures and additional internal signals have to be declared in the declaration part before they can be used in the implementation part.

A process can also use its own local variables, declared inside the process which uses them (schematically indicated by "Variable\_Declaration").

This causes the question whether to declare a global signal or a local variable for holding a value.

Figure 9: General VHDL program structure

- If the value is needed outside the process, it can only be held by a signal.

- Sequential computations within one cycle need variables. Sequential computations means: A process writes a value. Thereafter, the same process reads this updated value in the same cycle.

Signals own the property of having a delta-delay, which delays the update until the next cycle starts. Variables do not have this property and

therefore can be used in this case.

#### • Otherwise:

Declare a signal, if a physical equivalent (physical signal or wire) in the final hardware is expected.

Declare a variable, if the description is too abstract to have an obvious correspondence to hardware (variables in SFSMD).

An exception to the rule of leaving the entity unchanged is needed: When switching the models for the algorithm to deeper refinement levels, some synchronization signals like *start*, *done* and *clk* (clock) need to be added in the entity. They are inevitable ports of the final, hardware but they are not *data* ports.

In the figure, the words "Design\_Input" and "Design\_Output" are abbreviations. They stand for the range of all inputs and outputs of the design.

# 4 Describing the Models in VHDL

Section 1 gave a view of the meaning of the hardware description models. The following sections explain how to model them in VHDL and discuss some significant problems.

#### 4.1 Abstract and Introduction

#### 4.1.1 The State Machines Graphically

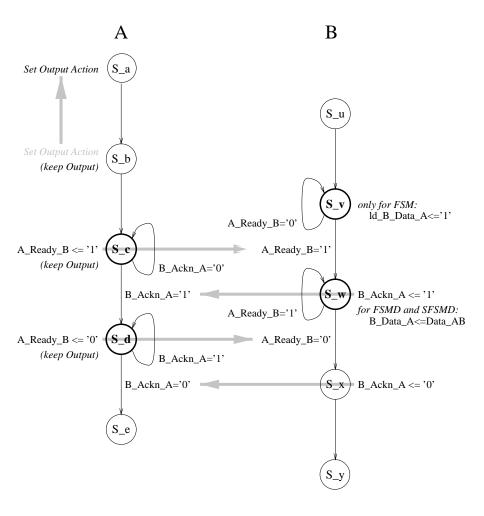

The graphical representation of the state machines in figures 10 and 11 is according to the following rules: The actions are attached to the states they are assigned or scheduled to. The kind and size of the actions is dependent on the model. The new data results caused by the actions are not available before the next state transition.

Among the arrows starting at the current state there must be exactly one with a true condition. Thisone determines the next state. All possibilities have to be covered by the conditions and ambiguity is not allowed.

Whereas state transitions are bound to conditions, actions are bound to states only but not to conditions. Such state machines are called *Moore Machines*.

#### 4.1.2 Translation into VHDL

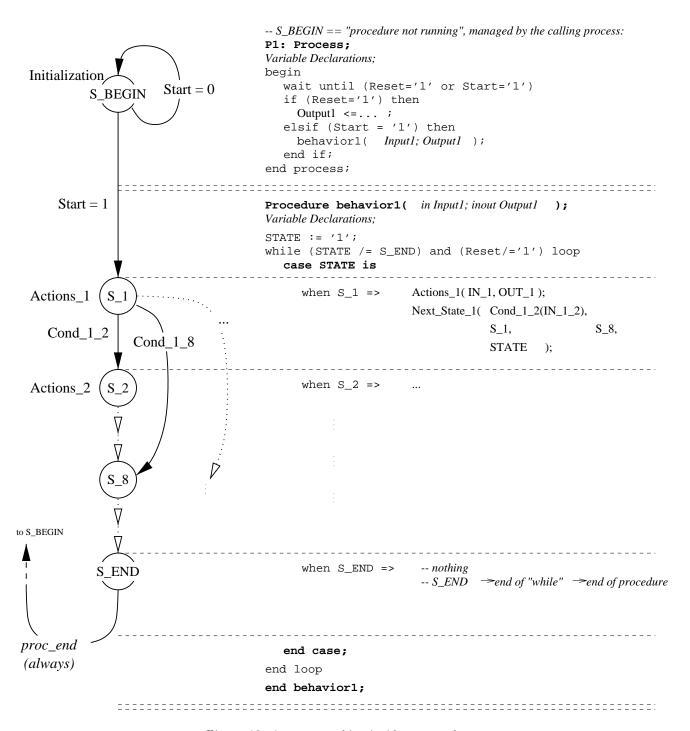

The right-hand side of figures 10 and 11 show possible VHDL descriptions, which implement the graphical representation of the right-hand side. Figure 10 shows how to implement a state machine inside a procedure. Figure 11 describes the implementation inside a process. Both versions use the VHDL-case statement for modeling the state machine.

In the figures, the typewriter font is used for direct VHDL code. Proportional font is used for parts which can either be a procedure (resp. function) or an abbreviation for a piece of code, that is:

#### Actions\_i:

Parts of the algorithm assigned to the state i. Actions\_i can be a piece of code or a procedure. It reads the signals/ variables represented by IN\_i and writes the variables represented by OUT\_i.

#### Cond\_i\_j:

Condition for the state transition from state i to j. Cond\_i\_j may be either a function or a piece of code. It reads variables and signals from IN\_i\_j. The result value of the condition is represented by its name itself.

#### Next\_State\_i:

Sets the value of **state** after state i. Next\_State\_i is an expression or a procedure. In the used syntax, it has the following parameters: inputs: list of conditions, list of possible next states; output: next state (STATE).

**Procedure versus Process.** The "procedure version" should be used for models at a high level of abstraction (SFSMD) and for models which do not use timing (SFSMD, FSMD Without Time).

Procedures are well-suited for sequential programming style with preferred use of variables instead of signals. This especially meets the requirements of SFSMD. Additionally, SFSMDs can be simply concatenated by calling one procedure after the other. This means, no allusions to a hardware protocol are needed.

A process on the other hand does not have these advantages. Additionally, a process is an endless loop which is developed for use with a clock.

Figure 10: A state machine inside a procedure

```

behavior1: Process(Clock)

Variable Declarations;

begin

if (Clock'event and Clock='1') then

if (Reset = '1') then

Initialization( OUT_1 );

next_STATE <= S_BEGIN;</pre>

else

case next_STATE is

when S_BEGIN => Done <= '0';

Initialization S_BEGIN Start = '0'

Initialization( OUT_1 );

if Start = '1'

then next_STATE<= S_1;

else next_STATE<= S_BEGIN;</pre>

Start = '1'

end if;

when S_1 =>

Actions_1( IN_1, OUT_1 );

Actions_1

Next_State_1( Cond_1_2, Cond_1_8,

S_2,

S_{8}

Cond_1_2

Cond 1 8

next_STATE );

when S_2 =>

Actions 2

when S_END => Done <= '1';

S END Start = '1'

Done:='1'

if Start = '0'

then next_STATE<= S_BEGIN;

to S_BEGIN

else next_STATE<= S_END;</pre>

end if;

end case;

Start = '0'

end if;

end if;

end process;

```

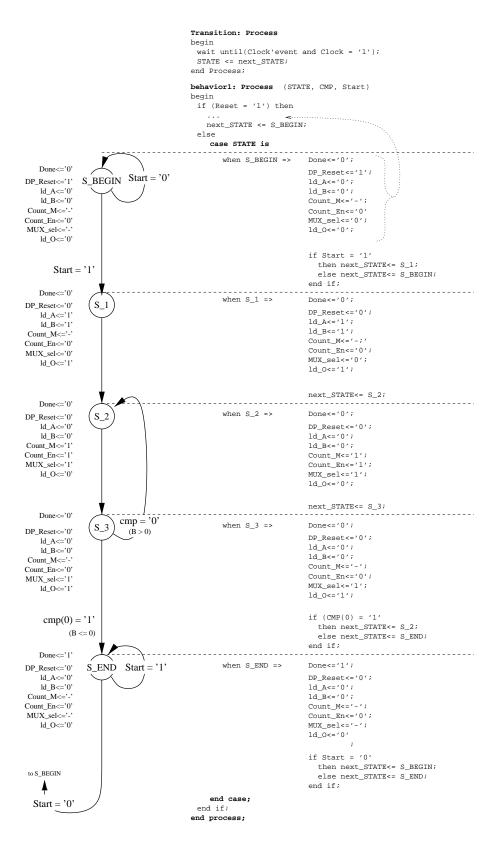

Figure 11: A state machine inside a process

Figure 12: A state machine for controlling a separate datapath

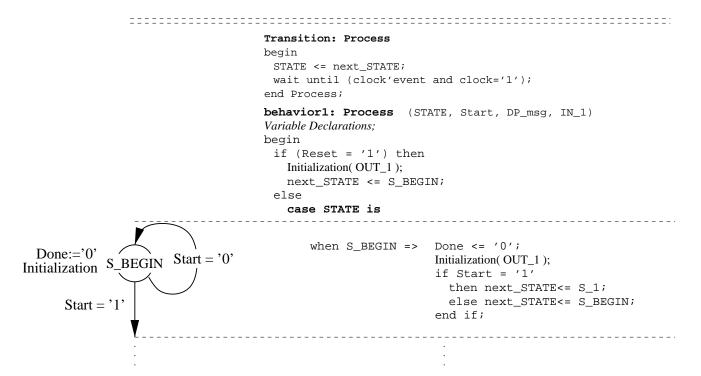

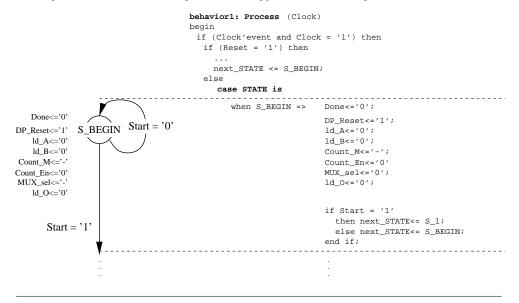

The "process version" is preferable if the model uses a clock (FSMD With Clock, FSM controlling datapath).

Although a procedure could be used with wait statements, this is not recommended. Such a bad style of hidden and scattered wait statements could confuse humans and synthesis machines. According to that, the even worse way of using wait statements inside a function is forbidden by the language already. Thus processes are better for use with a clocked description. The use of a sensitivity list in the process heads expose the wait conditions very well. In figure 11 the list has one entry: Clock.

Special Case: State Machine and Separate Datapath. Figure 12 shows some changes to figure 11: The activation of the next state is done by a newly introduced process. The second process, which contains the state machine, is made sensitive to the state and all input signals (process(STATE,Start,DP\_msg,IN\_1)). This modification is needed for a model which uses a separate datapath. It compensates delays which are caused by the datapath: In contrast to a single state machine with "build-in" datapath, a separate control-FSM just gives commands and the actual computations are ex-

ecuted by the datapath one cycle delayed.

The modification in figure 12, however, compensates this: The clock has been removed from the state machine. Instead, datapath feedback messages now appear in the sensitivity list of the state machine's process. Thus the state machine can react to changes on these signals without waiting for the next clock cycle. In this way the delay is "compensated". See section 4.2.6 for more.

#### 4.2 Examples and Guidelines

This section shows how to use and code the models with VHDL with the help of examples. Examples are much clearer than the abstract descriptions of the previous section. The examples can be used like templates. Figures 13 to 17 show the descriptions of the state machines in either a procedure or a process. Figures 20 to 23 show their embedding into a complete VHDL description. In this latter set of figures, the declaration of all variables and signals, needed for the examples, can be seen too.

Important rules are generalized and described. Executable files of the examples are available and listed in the appendix.

#### 4.2.1 SFSMD Behavioral

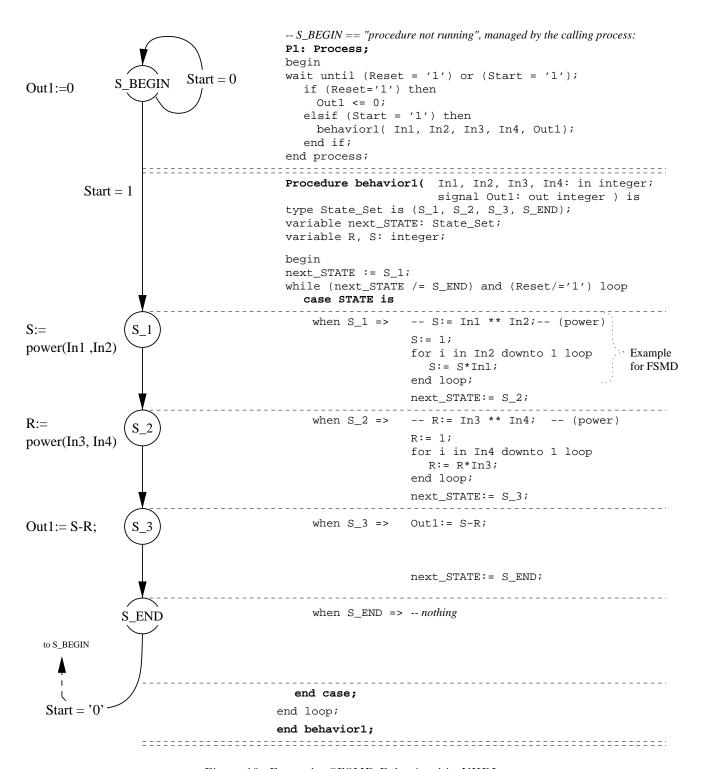

Figure 13 shows a very simple SFSMD: The superstates S\_1 and S\_2 perform expensive power operations each. In superstate S\_3, the results are subtracted.

This is just one way of describing the algorithm. The abstract model SFSMD provides a lot of freedom:

- The three superstates in the example may be merged into a single one.

- Actions and conditions (conditions are not used here, but see figure 10) can be of any complexity.

- In this example even the loop and the case statement may be omitted, because there is just a sequential computation:

```

begin

-- State S_1:

-- S:= In1 ** In2;

-- (power)

S := 1;

for i in In2 downto 1 loop

S := S * In1;

end loop;

-- State S_2:

-- R:= In3 ** In4;

-- (power)

R := 1:

for i in In4 downto 1 loop

R := R * In3;

end loop;

-- State S_3:

-- Output

Out1:=S-R;

end behavior1;

```

Rules. Almost all constructs of the programming language are allowed for use in the description of the SFSMD model, but the following rules have to be obeyed when modeling an SFSMD in VHDL:

• All inputs and outputs have to be declared clearly.

In VHDL, do not introduce "unofficial" data ports by reading from or writing to a file within a procedure. All inputs and outputs should be declared in the entity.

• Data ports have to be read and set accurately.

Other ports (control, timing) should be avoided.

An abstract description never means, that abstract results are allowed. To be a valid model, it

must occupy the data ports completely in accordance to the specifications, except that time is not handled. That means outputs are set without delay.

Synchronization ports and other timing related ports (like the clock input) are implementation specific. They are omitted in this model because this one is abstract and non-timing accurate.

In this model parallelism and timing are not used.

This means, in VHDL use only one process and prefer to use variables instead of signals.

Use of several parallel processes would mean switching to the model CHSFSMD (Concurrent Hierarchic SFSMD). In that model hierarchically higher processes start other processes parallelly. But this is not discussed here.

Signals should not be used because signal assignments used without appropriate timing delays are not executed in the desired sequential order (see section 3). It is difficult and dangerous to use signals in this model, because a large amount of sequential code is assigned to each superstate. The state is a variable, too.

#### 4.2.2 FSMD Behavioral

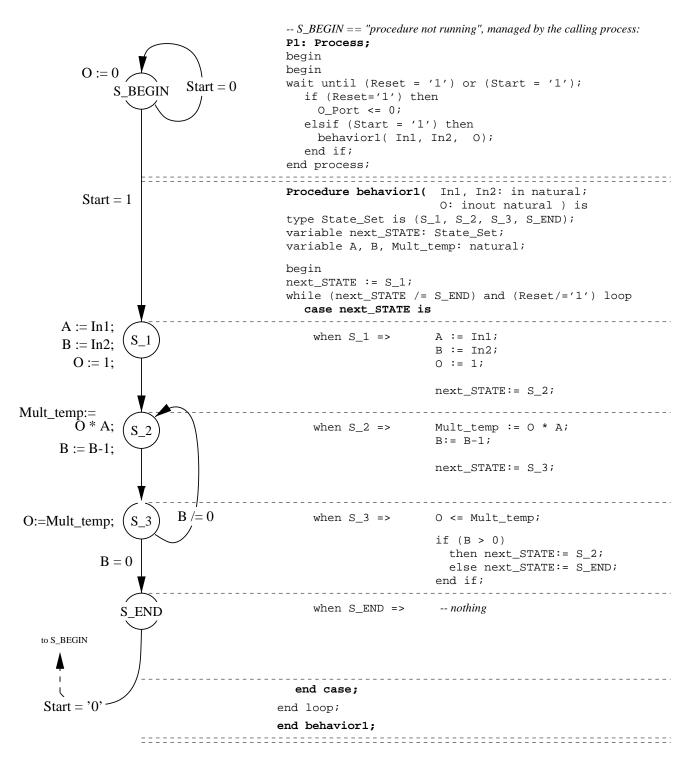

There are two variants of description for the model FSMD: FSMD Behavioral Without Time (figure 14) and FSMD Behavioral with clock (figure 15).

Timing and synchronization originally do not belong to this model, but introducing clock at this level often is an advantage when using VHDL. (See section "Discussion" below.)

The VHDL-implementations of both behavioral variants look similar: In this example, figures 14 and 15 implement superstate S\_1 of the SFSMD of figure 13. An FSMD also may implement several superstates.

**Steps.** The steps to convert a SFSMD into a FSMD are the following:

• Divide the SFSMD into slices which are meant to become implemented by a FSMD each.

A FSMD can be the implementation of just one superstate up to the whole SFSMD. After testing and/or refining into the model "FSM Controlling Datapath", the state machines can be joined together again by concatenating the

states (and merging the datapaths). Alternatively the state machines can remain separate when adding communication (see section 5).

• Choose way of description: FSMD Without Time or FSMD With Clock.

Usually the description with clock is preferable, when modeling in VHDL (see section "Discussion" below).

According to section 4.1.2, FSMD Without Time should be implemented in a procedure (figure 14). FSMD With Clock has to be implemented in a process (figure 15).

Version without time in a procedure:

- There doe not need to be a "when"statement for the state S\_BEGIN in this model.

- The reason is the sequential programming style: The state machine is alive only for the time it is needed, else it does not exist. If the code of the state machine is not executed, this means that it rests in the state S\_BEGIN.

- Inside the procedure only variables are used (assignment operator ":=").

(However, signals become inevitable in communicating state machines.)

- The simple data types are adopted from the SFSMD-model.

The example uses "integer" for instance.

Version using clock in a process:

- The states S\_BEGIN and S\_END as well as "start"- and "done"-signals are needed for synchronization.

- In a process, a state machine is always alive. The state machine waits in state S\_BEGIN for its "start"-signal. When the machine finishes, it reaches the state S\_END and sets a "done" signal.

- In the process, signals are used generally.

(Variables may be used exceptionally, if they are not expected to have a corresponding wire or register in the final hardware, e.g. variables which model delay.)

- The hardware related data type std\_logic\_vector is used in the example.

This seems likely because this description

uses clock which is close to hardware, too. Both aspects provide the possibility of easy translation into the model "FSM Controlling Datapath".

#### • Schedule the operations:

A superstate is broken into several states for FSMD. Each state of a FSMD lasts exactly one cycle time. A state of a FSMD can contain as many computations as the data dependencies allow. However a lot of computations in a state cause the datapath to become large (see section scheduling).

In the example, the superstate S\_1 in figure 13 is scheduled to the states S\_1 to S\_3 in figures 14 and 15. The "power"-operation of the superstate cannot be executed in one cycle. Hardware usually performs this operation by running a loop of multiplications. So does this FSMD example.

# 4.2.3 Discussion: FSMD Behavioral without time or with clock

The constraint of using variables for behavior input and output is not nice. Behavior input and outputs as well as many other value-holders<sup>1</sup> can be expected to have a physical equivalence (wire) in the final hardware. Therefore the use of signals would be more accurate.

A more unpleasant circumstance is the fact, that in a description without clock, a VHDL Simulator determines the execution time equal to zero. Therefore the possibilities for debugging the code are limited to the old fashioned way of running the code step by step. When simulating hardware, displaying the data and the clock cycles over the time may be desired. That is not possible, because there is no time. This disadvantage can be removed by using FSMD Behavioral with clock. In this description a clock accurate simulation shows much better how the design will work. (Example: The "Waveform Viewer" provided by "Synopsys" can be employed now.) Debugging becomes easier. Additionally, the designer already sees, where to pay attention to possible timing problems.

Using the appropriate subset of VHDL, the model FSMD Behavioral with clock can be even directly synthesizable already (with bad results though, compared to "FSM Controlling Datapath").

A theoretical disadvantage of this model is the fact, that hardware details like clock normally belong to a

$<sup>^1\,</sup>Value\text{-}h\,older$  is used as a generic term for both VHDL- signal and VHDL- variable .

structural description instead of to a behavioral one, because it is an implementation detail. However, this step has to be performed anyway and besides the advantages for simulation, this makes the step to the description "FSM Controlling Datapath" closer.

Finally, such allusions to hardware implementations are just *suggestions* and *not definite*. It still has to be regarded as being a *behavioral* description. The used clock time may change or become a multiple of the real system clock.

It also is possible to use both behavioral models, first the one without clock and then refine it to the one with clock.

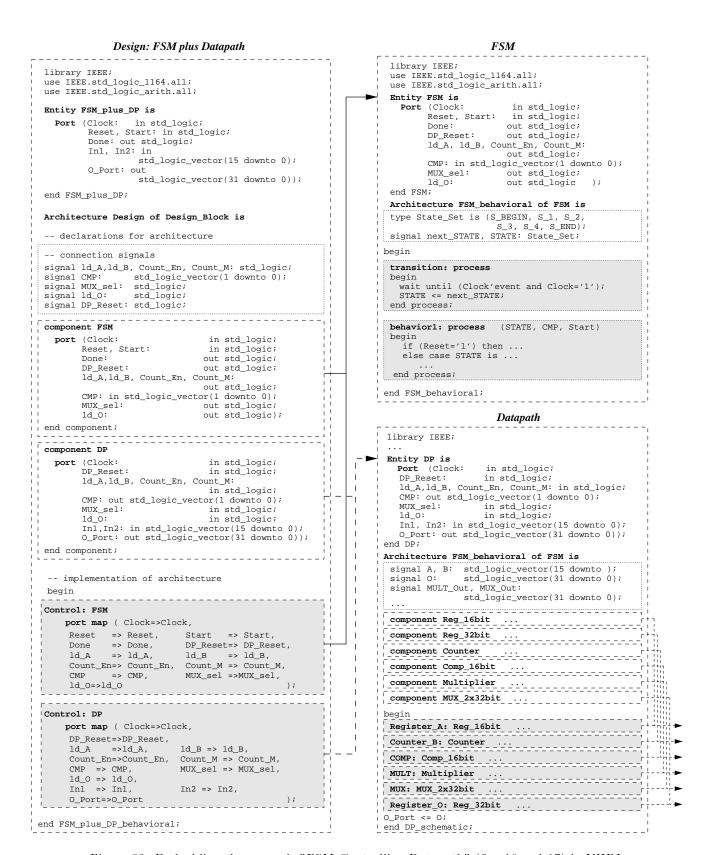

#### 4.2.4 FSM Behavioral Controlling Datapath Structural

After the FSMD Behavioral description with clock is finished, the step to a structural datapath controlled by a FSM is easily described, but tedious to perform.

- A VHDL datapath file has to be created, which binds the library components<sup>2</sup> and connects the entity signals (data in- and outputs, control inputs and message outputs). See figure 16.

- All computations and data assignments are removed from the state machines, including computations within conditions. Instead, the appropriate control signals, which cause the data processing in the datapath, are set. See example in figure 17.

- The state machine is notified of the result of conditions by message signals, only few bits wide ("CMP" in figure 16).

- A separate process for setting the next state has to be introduced.

- The remaining process for the FSM is not clock-triggered any longer, but sensitive to all inputs of the FSM. (See sensitivity list in the process's head.) Thus this process can react to results of the datapath *before* the next clock edge arrives and "compensate" the delay of the datapath (see section 4.2.6 below).

- A datapath structural description has to be got. This is a deep refinement level. All wires and hardware blocks are specified. Therefore only signals have to be used and the use of variables is forbidden here. Components of the datapath are instantiated as shown in figure 16 by an example.

#### 4.2.5 FSM Structural Controlling Datapath Structural

In most cases, the step from behavioral FSM to structural FSM does not need to be supervised by humans. Figure 18 shows the conversion into a structural description. Each bit of the output of the FSM is a boolean function of all bits.

The example shows the unoptimized coding. The size of the boolean functions should be minimized before synthesis.

#### 4.2.6 Compensation of Datapath Delay

An FSMD does computation directly. For example, in figure 14, the state S\_2 contains Mult\_temp := 0 \* A. In contrast to that, a control-FSM just gives commands.

The actual computations are executed by the datapath one clock cycle delayed. As a result, a FSMD could not simply be translated into "FSM Controlling Datapath". The solution is a modification in figure 12 which is shown in figure 17. As soon as the datapath gives its result, the FSM is employed again within the same clock cycle because of the feedback messages appearing in the sensitivity list. In figure 17 there is just one feedback signal: CMP.

Thus the datapath delay is "compensated" and computation results can be used one cycle after they were ordered. The behavior of "FSM Controlling Datapath" is back to the expected behavior of a state machine. It is equivalent to the behavior of the FSMD, from which it is derived and in accordance with the FSM architecture on the left-hand side of figure 8 in section 1.3.3.

Note on "compensation":

When talking about "compensation" here, it does not mean a real removal of the delay. Delays and actions are just moved closer together. This causes a decrease of the allowed clock period time!

Warnings:

• Omitting the separation of next-state process and state-machine process means, the delay through the datapath will not be compensated. This is equivalent to introducing additional output latches as shown in figure 19. Doing this is possible, but discouraged. It means a change of common architecture agreements and the behavior is not equivalent to the FSMD-model.

<sup>&</sup>lt;sup>2</sup>from user libraries and /or propriatary libraries

• Introducing a separate next-state process in the FSMD-model itself is strictly forbidden! Trying to compensate non-existent delays means removing necessary latches. Unlatched, indeterministic feedback loops may occur. Also, such a description can never be translated into "FSM Controlling Datapath" any more.

Figure 13: Example: SFSMD Behavioral in VHDL

Figure 14: Example: FSMD Behavioral Without Time in VHDL

```

behavior1: Process(Clock)

begin

if (Clock'event and Clock='1') then

if (Reset = '1') then

0 <= (others=>'0');

next_STATE <= S_BEGIN;</pre>

else

case next_STATE is

when S_BEGIN => Done <= '0';

S_BEGIN Start = '0'

Done<='0'

if Start = '1'

then next_STATE<= S_1;

else next_STATE<= S_BEGIN;</pre>

Start = '1'

end if;

A \leq In1;

when S_1 =>

A <= In1;

B \leq In2;

B <= In2;

O \le 1;

0 <= conv_std_logic_vector(1, 32);</pre>

next_STATE<= S_2;

_____.

Mult_temp<=

when S_2 =>

Mult_temp <= O(15 downto 0) * A;</pre>

O*R;

B <= B - conv_std_logic_vector(1, 1</pre>

B \leq In2;

next_STATE<= S_3;</pre>

B > 0

when S_3 =>

O <= Mult_temp;</pre>

O<=Mult_temp;

if (B > conv_std_logic_vector(0, 16

then next_STATE<= S_2;

B \le 0

else next_STATE<= S_END;</pre>

end if;

Done <= '1';

when S_END =>

Start = '1'

Done<='1';

S END

if Start = '0'

to S_BEGIN

then next_STATE<= S_BEGIN;

else next_STATE<= S_END;</pre>

end if;

end case;

end if;

Start = '0'

end if;

end process;

```

Figure 15: Example: FSMD Behavioral With Clock in VHDL

Figure 16: Example: Datapath of "FSM Behavioral Controlling Datapath Structural"

Figure 17: Example: FSM of "FSM Behavioral Controlling Datapath Structural"

```

Clock

Reset

Enable

State Register

STATE

```

#### State\_Register: Process(Clock, Enable)

```

begin

if (Clock'event and Clock = '1') then

if (Reset = '1') then STATE <= 000;

elsif (Enable = '1') then STATE <= next_STATE;

end if;

end if;

end Process;</pre>

```

|       | DP-Control and Status Output Logic                                 |               |  |  |  |

|-------|--------------------------------------------------------------------|---------------|--|--|--|

| Input | DP-Control Output                                                  | Status Output |  |  |  |

| STATE | DP_Reset<br>1d_A<br>1d_B<br>Count_M<br>Count_En<br>MUX_sel<br>1d_0 | Done          |  |  |  |

| 000   | 1 0 0 0 0                                                          | 0             |  |  |  |

| 000   | 1 0 0 - 0 - 0                                                      | 0             |  |  |  |

| 001   | 0 1 1 - 0 0 1                                                      | 0             |  |  |  |

| 010   | 0 0 0 1 1 1 0                                                      | 0             |  |  |  |

| 011   | 0 0 0 - 0 1 1                                                      | 0             |  |  |  |

| 111   | 0 0 0 - 0 - 0                                                      | 1             |  |  |  |

| rest  | don't care                                                         | don't care    |  |  |  |

#### -- Datapath-Control and Status Output Logic

```

-- Datapath Control Output

DP_Reset <=

( not STATE(2) and not STATE(1) and not STATE(0) );

ld_A

<=

( not STATE(2) and not STATE(1) and

STATE(0));

ld_B

<=

( not STATE(2) and not STATE(1) and

STATE(0));

Count_M

<=

( not STATE(2) and

STATE(1) and not STATE(0) );

Count_En <=

( not STATE(2) and

STATE(1) and not STATE(0) );

MUX_sel

<=

( not STATE(2) and

{\tt STATE(1)} and not {\tt STATE(0)} )

OR ( not STATE(2) and

STATE(1) and

STATE(0));

ld 0

( not STATE(2) and not STATE(1) and

STATE(0))

OR ( not STATE(2) and

STATE(1) and

STATE(0));

-- Controller Status Output

STATE(2) and

STATE(1) and

STATE(0));

Done

<= (

```

| Input                           |                      |                       | Next-State Logic Output         |

|---------------------------------|----------------------|-----------------------|---------------------------------|

| STATE                           | CMP                  | Start                 | next_STATE                      |

| 000<br>000<br>001<br>010<br>011 | <br><br><br>-1<br>-0 | 0<br>1<br>-<br>-<br>- | 000<br>001<br>010<br>011<br>010 |

| 111<br>rest                     |                      | -                     | don't care                      |

```

-- Next-State Logic

next_STATE(2) <= ( not STATE(2) and STATE(1) and next_STATE(1) <= ( not STATE(2) and not STATE(1) and

STATE(0) and not CMP(0) );

STATE(0))

OR ( not STATE(2) and

STATE(1) and not STATE(0) )

OR ( not STATE(2) and

STATE(1) and

STATE(0) and

OR ( not STATE(2) and

STATE(1) and

STATE(0) and not CMP(0));

next_STATE(0) <=

( not STATE(2) and not STATE(1) and not STATE(0) and START )

OR ( not STATE(2) and

STATE(1) and not STATE(0)

OR ( not STATE(2) and

STATE(1) and

STATE(0) and not CMP(0));

```

Figure 18: Example: FSM of "FSM Structural Controlling Datapath Structural"

a) Changes in FSM Behavioral Description when Using just One Process (Outputs Latched)

b) Equvalent Changes in FSM Structural Description / Changes of the former Architecture (Outputs Latched)

```

Next State Register: Process(Clock, Enable)

begin

if (Clock'event and Clock='1') then

if (Reset='1') then next_STATE <= "000";

elsif (Enable='1') then next_STATE <= next_STATE_logic;</pre>

end if;

end Process;

Output_Registers: Process(Clock, Enable)

begin

Control Inputs (Start)

if (Clock'event and Clock='1') then

(Reset='1') then

DP_Reset <= '1';

Next-State

ld_A<='0';

Logic

ld_B<='0';

Clock

Count_M<='0';

Reset

Data-

Next-State Reg

Count_En<='0';

Enable

path

MUX sel<='0';

Control

ld 0<='0';

Datapath

Done <= '0';

Control

else

and

DP_Reset <= DP_Reset_Logic;</pre>

Output Logic

ld_A <= ld_A_Logic;

ld_B <= ld_B_logic;</pre>

Output Reg's

Count_M <= Count_M_Logic;

Count_En <= Count_En_Logic;

MUX_sel <= MUX_sel_Logic;

Control Outputs (Done)

ld_0 <= ld_0_Logic;</pre>

Done <= Done_Logic;

end if;

end if;

end Process;

-- Datapath-Control and Status Output Logic

DP_Reset_Logic <= ( not STATE(2) and not STATE(1) and not STATE(0) );</pre>

ld_A_Logic <= ...

-- Next State Logic

\texttt{next\_STATE\_Logic(2)} \  \, <= \  \, (\texttt{not} \  \, \texttt{STATE(2)} \  \, \texttt{and} \  \, \texttt{STATE(1)} \  \, \texttt{and} \  \, \texttt{STATE(0)} \  \, \texttt{and} \  \, \texttt{not} \  \, \texttt{CMP(0)} \  \, );

next STATE Logic(1) <= ...

```

Figure 19: Warning: Omitting separation of next-state-process causes additional output latches

#### Design: SFSMD Example

```

-- no library needed

Entity SFSMD_ex is

port (Reset, Start:

in bit;

In1, In2, In3, In4:in integer;

Out1:

out integer );

end SFSMD ex;

Architecture SFSMD_ex_behavioral

of SFSMD_ex is

-- declarations for architecture

-- no add. signal declarations needed

Procedure behavior1

(In1, In2, In3, In4: in integer;

signal Out1: out integer)

type State_Set is (S_1, S_2, S_3, S_END);

variable next_STATE: State_Set;

variable R, S: integer;

begin

-- implementation of architecture

P1: process

end SFSMD_ex_behavioral;

```

Figure 20: Embedding the example SFSMD (fig. 13) in VHDL

#### Design: FSMD "No Time" Example

```

- no library needed

Entity FSMD_no_time_ex is

port (Reset, Start: in bit;

In1, In2:

in natural;

out natural );

O Port:

end FSMD_no_time_ex;

Architecture FSMD_no_time_ex_behavioral

of FSMD_no_time_ex is

-- declarations for architecture

-- behavior outputs

signal O: natural;

_____

Procedure behavior1

(In1, In2: in natural;

signal O: inout natural)

type State_Set is (S_1, S_2, S_3, S_END);

variable next_STATE: State_Set;

variable A, B: natural;

variable Mult_temp: natural;

begin

-- implementation of architecture

P1: process

-- Entity Outputs

O_Port <= 0;

end FSMD_no_time_ex_behavioral;

```

Figure 21: Embedding the example FSMD Without Time (fig. 14) in VHDL

#### Design: FSMD "with Clock" Example

```

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

Entity FSMD_clock_ex is

port (Clock: in std_logic;

Reset, Start: in std_logic;

Done: out std_logic;

In1, In2: in unsigned(15 downto 0);

O_Port: out unsigned(31 downto 0));

end FSMD_clock_ex;

Architecture FSMD_clock_ex_behavioral

of FSMD_clock_ex is

-- declarations for architecture

signal O: unsigned(31 downto 0);

signal Mult_temp: unsigned(31 downto 0);

type State_Set is (S_BEGIN, S_1, S_2,

S_3, S_END);

signal next_STATE: State_Set;

signal A, B: unsigned(15 downto 0);

-- implementation of architecture

begin

behavior1: process

(Clock)

-- Entity Outputs

O_Port <= 0;

end FSMD_clock_ex_behavioral;

```

Figure 22: Embedding the example FSMD With Clock (fig. 15) in VHDL

Figure 23: Embedding the example "FSM Controlling Datapath" (fig. 16 and 17) in VHDL

# 5 Communication of State Machines

State machines may have to exchange data. There can be different reasons for having state machines which need to communicate:

- A large super state machine can be divided into smaller state machines in order to get smaller problems.

- Separate state machines can be designed, which solve common problems. They may be required for use in connection with other state machines like "plug-ins".

- A state machine may have to be divided, when it contains problems with different demands of the implementation platform. Each piece then can run on the platform which is best.

In all these cases, data exchange between the several state machines is necessary and an appropriate protocol needs to come along with it. In the following subsections, the simple method of handshaking is discussed, which is sufficient for many problems. Single handshake can be used, if the communicating state machines have the same cycle time. However double handshake is recommended, since it works with all odd cycle times and even if there is no assigned cycle time (SFSMD and FSMD Without Time).

A data sending machine may produce bursts of data with delays between the bursts. Also the receiving machine may consume the data irregularly. In these cases a buffer comes in handy, which can be a queue or a memory for instance. The design of state machines, exchanging data via a queue or memory, is shown in the later sections.

#### 5.1 Single Handshake

A prerequisite for single handshake is that each state machine is either a FSMD, which uses clock, or a FSM, both working with the same clock.

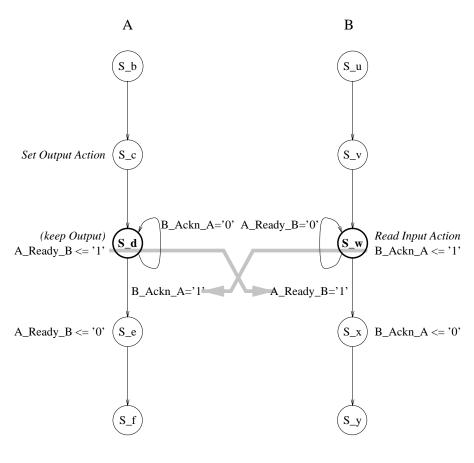

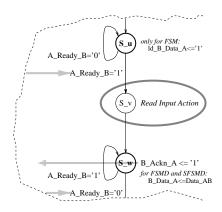

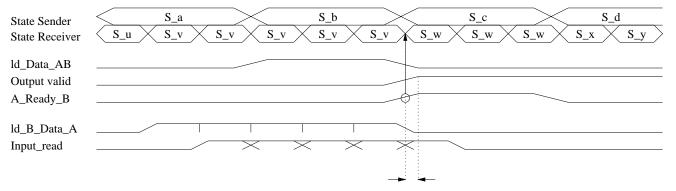

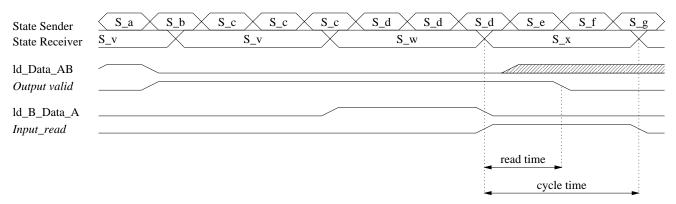

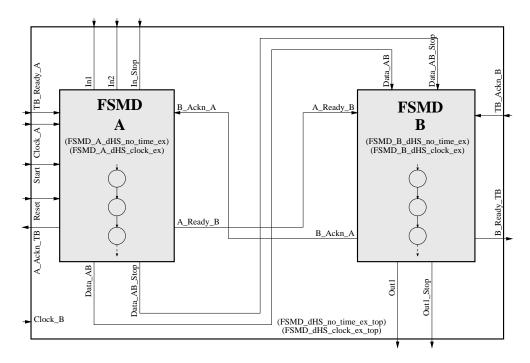

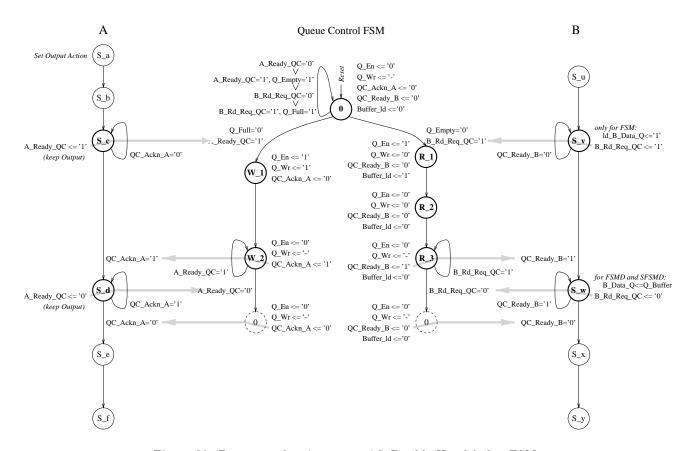

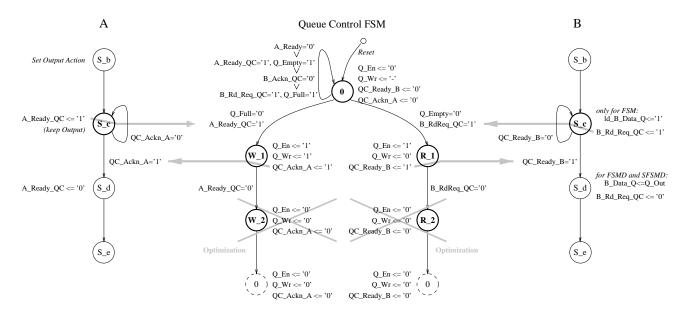

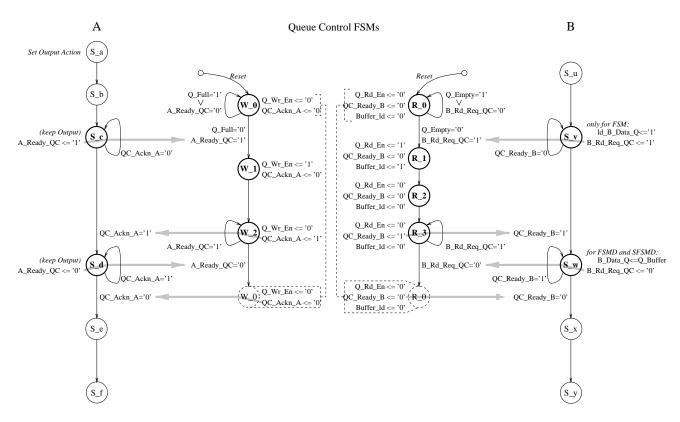

Figure 24 shows the usage of signals for single handshake between two state machines. Set-output and read actions are adapted to FSMD or FSM according to the table below the figure. If the sender (A) is a FSMD, the Output is set in state S\_c directly. If it is a FSM, the associated datapath sets the output one cycle delayed, in state S\_d. The signal A\_Ready\_B is set to '1', when the state machine has set the output or just sets it. This means, one cycle after A\_Ready\_B was set, the data can be read by the receiver (B). The

receiver gives the acknowledge signal B\_Ackn\_A when it reads the data.

Note, that the receiver may reach state S\_w earlier than data is send. Then it reads invalid data. But, the signal A\_Ready is '0' as long as the data is invalid. This causes the receiver to read the data again and again until it finally reads valid data.

If the receiver is an FSM, reading is delayed by the datapath, too. However, reading the data in state S\_x is early enough, since both state machines work synchronously with the same clock.

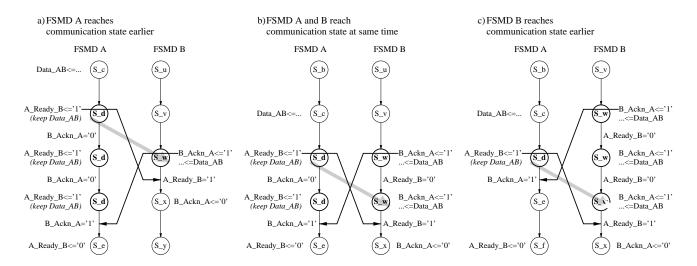

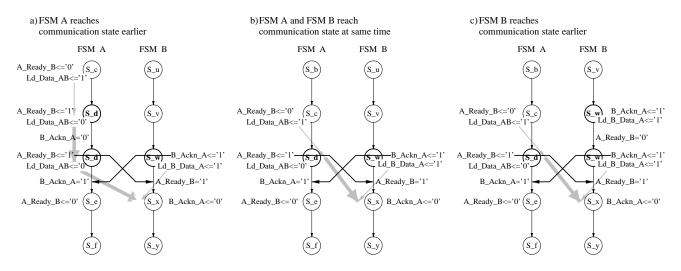

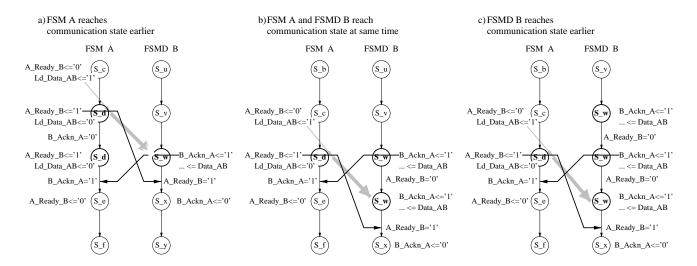

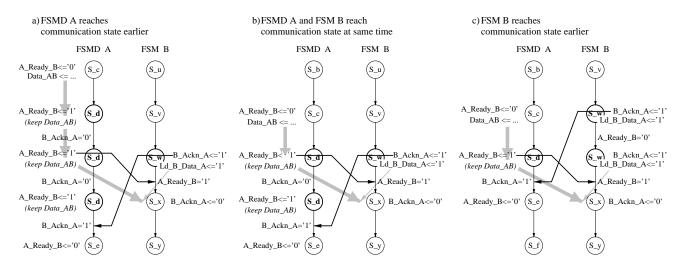

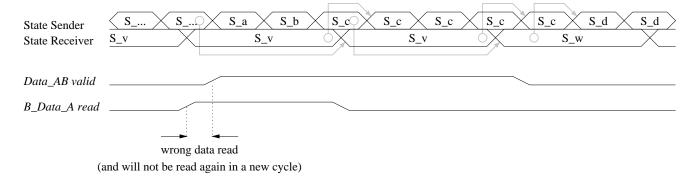

Figures 25 to 28 show the order of events and switching of states for all possibilities: Figures for FSMD-FSMD, FSM-FSM, FSM-FSMD and FSMD-FSM each contain diagrams for the following three cases: A is earlier than B, A and B reach the communication states at the same time, B is earlier than A (where A is sender and B is receiver).

Black arrows show how ready and acknowledge signals cause state transitions. A FSMD model cannot recognize the setting of a signal within the same cycle but only in the next cycle. This causes the large "scissors" in figure 25.

In the model "FSM Controlling Datapath", a side effect of compensating the datapath-delay is the early reaction to the input signals. The results are the smaller, narrow "scissors" in figure 26.

Figures 27 and 28 show the connection of FSM with FSMD, resulting in a mixture of the two types of "scissors".

In the FSMs, thin gray arrows indicate the wait period for setting and reading data by the datapath. The compensation of the datapath delay, stated in section 4.2.6, does not apply for synchronous data-transfer via the ports. The compensation just compensates a delayed reaction of the FSM within the same design.

Thick gray arrows point out, how many cycles after the actual setting of the data, it is read. This number must be greater than or equal to one, meaning the arrow must point downwards. A horizontal arrow is not allowed. If the thick arrows point downwards through several states, the output data has to be kept in these states.

The timing diagrams show the functionality of the construct in figure 24.

The appendix contains figures with statemachines transmitting data via a queue by single handshake. This is not discussed further, because the focus is set on the more robust and adaptive double handshake. For explanation about a queue, refer to section 5.3.2.

|                    | FSMD (with clock)     | FSM (of FSM+Datapath) |

|--------------------|-----------------------|-----------------------|

|                    | Set / Read Ports      | Load Registers        |

| Set Output Action  | Data_AB <=            | Ld_Data_AB <= '1'     |

| Read Output Action | n B_Data_A <= Data_AB | Ld_B_Data_A <= '1'    |

Figure 24: Single Handshake

Figure 25: Cases, when using Single Handshake with two FSMD

Figure 26: Cases, when using Single Handshake with two FSM

Figure 27: Cases, when using Single Handshake with a FSM transmitting to a FSMD

Figure 28: Cases, when using Single Handshake with a FSMD transmitting to a FSM

#### 5.2 Double Handshake

Double handshaking makes the data exchange much more robust and works with all kinds of cycle times.

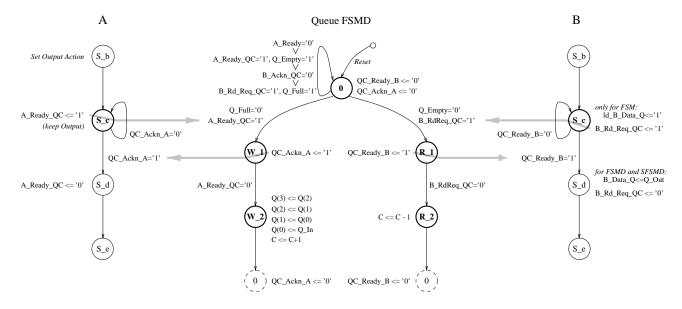

See figure 30. First, similar to the simple handshake, the sender puts data on its output port and sets the ready signal (A\_Ready\_B='1'). The receiver reads the data and acknowledges it by B\_Ackn\_A='1'. Then a second handshake follows: The sender sets A\_Ready\_B to '0' and waits for a B\_Ackn\_A='0' from the receiver. This assures that none of the state machines can run ahead of the other one:

If the receiver would not wait in state S\_w for A\_Ready\_B to become '0' again, it would not be able to know when the sender has noticed that the data has been received. There is the danger of removing the received confirmation signal B\_Ackn\_A too early. If the sender would not wait in state S\_d for B\_Ackn\_A to be '0' again, it may start another data exchange in some other state and read the old B\_Ackn\_A='1'.

Figure 30 also assures, that the signal A\_Ready\_B='1' at earliest is set one cycle after the output signal has been set. Both signals cannot be set at the same time, because in an asynchronous communication, it is unknown which one would be recognized first by the receiver.

In the same way, the output signal must remain valid until the next receiver-cycle after the read operation. In figure 30, this is *not* done by moving B\_Ackn\_A <= '1' to a later cycle. Instead the output of A is held until B\_Ackn\_A = '0'. Doing so saves additional states.

The reaction delay of a datapath makes it necessary to move the "set output operation" within state machine A from state S\_b to state S\_a. State S\_a can be used as a "generalized set output state", which works for all models.

The delay of the datapath has to be considered in the receiving state machine, too. Here, a "generalized" state is impossible without introducing another state (figure 29). If no extra state is introduced, the output action has to be moved, depending on the used model (see figure 30):

SFSMD, FSMD: use state S\_w: B\_Data\_A<=Data\_AB; FSM: use state S\_v: ld\_B\_Data\_A<='1'.

Figures 31 and 32 demonstrate the timing problems which may occur, if output action and input action are not scheduled at the right state.

Figure 32b also shows that a FSMD determines its next state when entering a state. An FSM, however, updates its "next state"-value continuously during the the current cycle. Thus, communication between FSMs uses less clock cycles. Double handshake

does not guarantee a specific number of cycles. It just assures a safe exchange of data.

Figure 29: Insertion of a "General State" in the receiving state machine of figure 30

|                    | SFSMD / FSMD        | FSM (of FSM+D)     |

|--------------------|---------------------|--------------------|

|                    | Set / Read Ports    | Load Registers     |

| Set Output Action  | Data_AB <=          | Ld_Data_AB <= '1'  |

| Read Output Action | B_Data_A <= Data_AB | Ld_B_Data_A <= '1' |

Figure 30: Double Handshake

a) For the state machines being FSMs, assume the write command is given in state S\_b instead of state S\_a. The following problem may occur, if the reading machine runs much faster than the writing machine:

Output may not be valid when it is read again for the final time.

Figure 31: Timing problem when writing

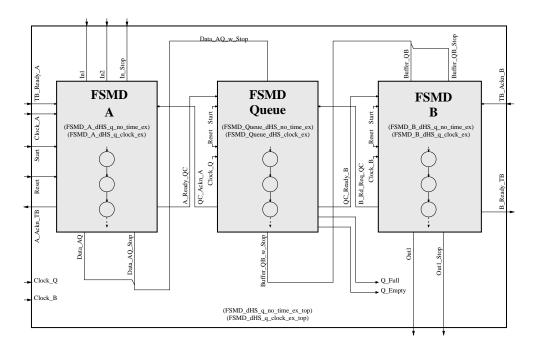

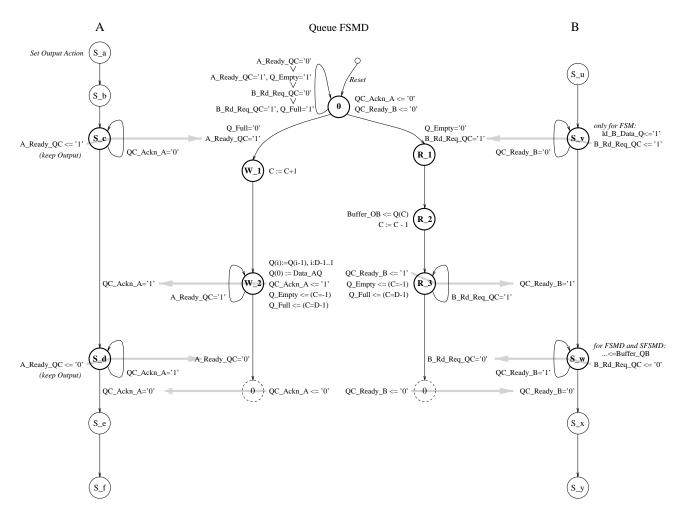

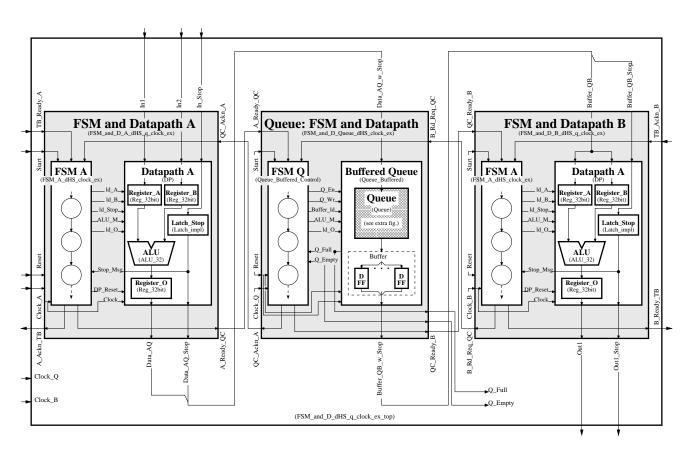

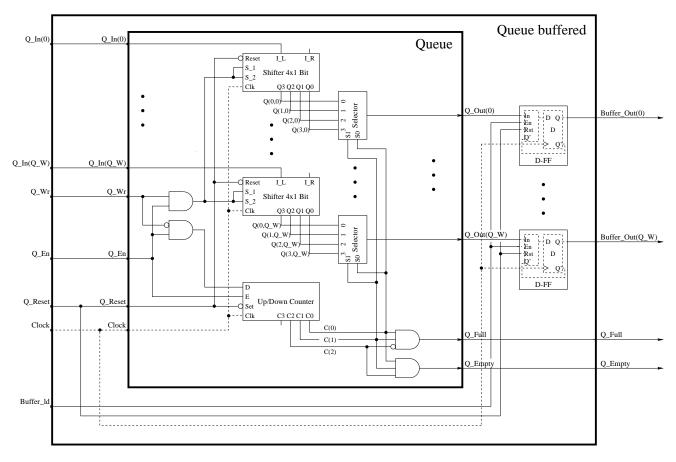

a) For the state machines being FSMs, assume the read command is given in state S\_w instead of state S\_v. The following problem is caused, if the writing machine runs much faster than the reading machine: