# Architettura degli Elaboratori Esercizi sul progetto di banchi di memoria

## **Davide Quaglia**

#### Dipartimento di Informatica – Università di Verona

#### **Esercizio 1**

Si realizzi un banco di memoria statica di 4MByte indirizzabile al byte utilizzando chip 1Mx1. Definire la composizione degli indirizzi di memoria.

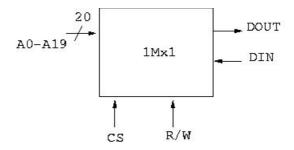

I chip 1Mx1 contengono 1M=2<sup>20</sup> bit e quindi hanno 20 bit di indirizzo.

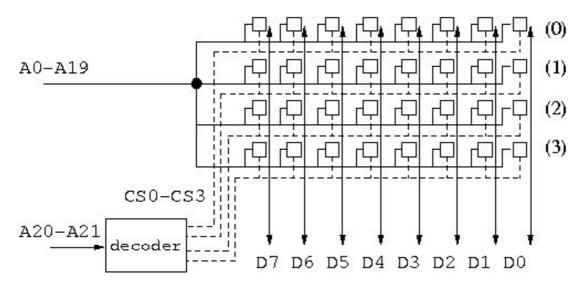

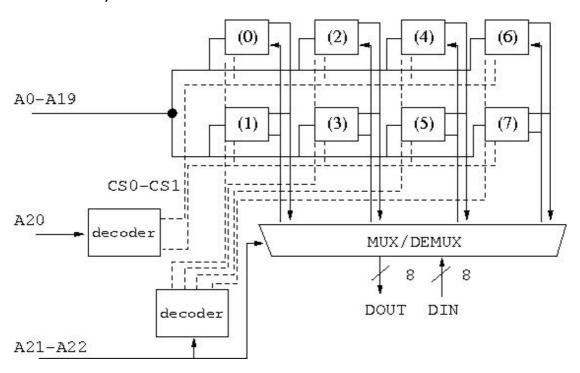

Il banco di memoria avra' invece 22 linee di indirizzo essendo 4M=2<sup>22</sup> Lo schema del banco di memoria e' il seguente:

Tra parentesi e' indicato l'ordine di lettura/scrittura al crescere degli indirizzi.

Gli indirizzi sono composti nel modo seguente:

| 21 20                              | 19                            | ) |

|------------------------------------|-------------------------------|---|

| Selezione<br>della riga di<br>chip | Indirizzo per il singolo chip |   |

#### Esercizio 2

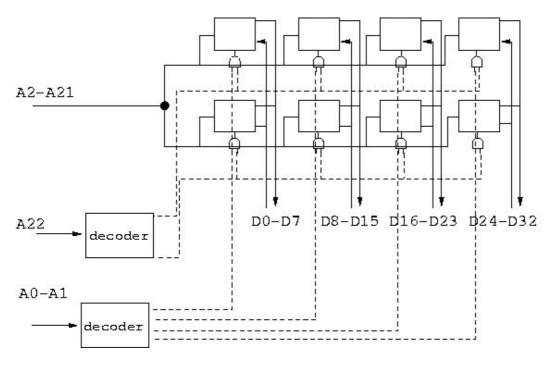

Si realizzi un banco di memoria statica di 2Mx32 indirizzabile al byte utilizzando chip 1Mx8. Definire la composizione degli indirizzi di memoria.

I chip 1Mx8 contengono 1M= $2^{20}$  byte e quindi hanno 20 bit di indirizzo. Il banco di memoria avra' invece 23 linee di indirizzo dovendo indirizzare 2Mx4byte = 8MB essendo 8M= $2^{23}$

#### Soluzione A)

Dentro i chip e' indicato l'ordine di lettura/scrittura al crescere degli indirizzi.

La composizione degli indirizzi e' la seguente:

#### Soluzione B)

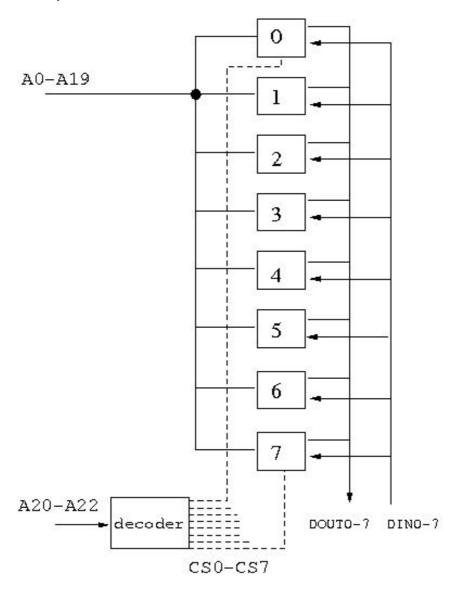

Tra parentesi e' indicato l'ordine di lettura/scrittura al crescere degli indirizzi.

La composizione degli indirizzi e' la seguente:

| 22  | 21 | 20                                 | 19                    | 0 |

|-----|----|------------------------------------|-----------------------|---|

| MUX |    | Selezione<br>della riga di<br>chip | Indirizzo per il chip |   |

ATT: e' necessario un decoder di colonna in fase di scrittura per evitare di azzerare le colonne non interessate dalla scrittura.

### Soluzione C)

La composizione degli indirizzi e' la seguente:

| 22                                 | 21                    | 2 | 1                                       | 0 |

|------------------------------------|-----------------------|---|-----------------------------------------|---|

| Selezione<br>della riga di<br>chip | Indirizzo per il chip |   | Selezione<br>della<br>colonna o<br>chip |   |

#### NOTA:

Nelle Soluzioni (A) e (B) si assume che il bus dati del sistema sia a 8 bit. Nella Soluzione (C) si assume che il bus dati del sistema sia a 32 bit e che il byte indirizzato venga messo sul bus nella sua posizione esatta rispetto alla parola di 32 bit che lo contiene (le linee del bus non interessate rimangono in alta impedenza).

#### Esercizio 3

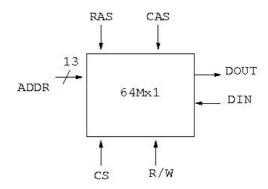

Si realizzi un banco di memoria dinamica 256Mx8 indirizzabile al byte utilizzando chip di memoria dinamica 64Mx1. Definire la composizione degli indirizzi di memoria.

I chip 64Mx1 contengono 64M=2<sup>26</sup> bit e quindi hanno bisogno di 26 bit di indirizzo. Siccome e' disagevole mettere cosi' tanti piedini in un chip, le memorie dinamiche richiedono di specificare l'indirizzo in due fasi dimezzando cosi' il numero di piedini necessari.

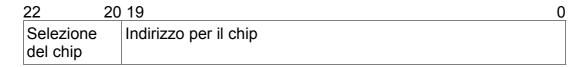

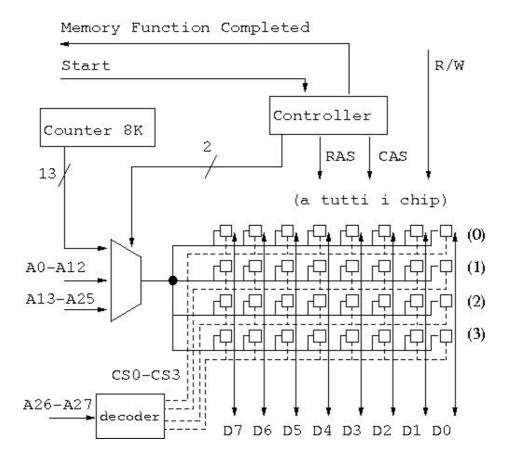

Il banco di memoria avra' invece 28 linee di indirizzo essendo 256M=228

Lo schema del banco di memoria risultante e' il seguente:

Tra parentesi e' indicato l'ordine di lettura/scrittura al crescere degli indirizzi. Si notino inoltre il multiplexer degli indirizzi, il controllore e il contatore modulo 8k che fornisce gli indirizzi di riga per rinfrescare la memoria (infatti e' suffciente leggere la riga per rinfrescarla completamente). I segnali RAS, CAS e R/W vanno direttamente a tutti i chip.

Gli indirizzi sono composti nel modo seguente:

| 27 26                              | 3 25                          | 0 |

|------------------------------------|-------------------------------|---|

| Selezione<br>della riga<br>di chip | Indirizzo per il singolo chip |   |