# Progetti laboratorio SPA

Laboratorio di Sistemi per la Progettazione Automatica A.A. 2005/2006 Nicola Bombieri

# (EDALab

- Ogni progetto deve essere sviluppato nei seguenti passi:

- 1. Realizzazione modulo IP in codice VHDL a livello RT.

- 2. Realizzazione testbench per la verifica preliminare.

- 3. Sintesi del codice prodotto verso il livello Gate.

- 4. Verifica del codice sintetizzato.

- 5. Documentazione.

- Punti extra:

- Descrizione del modulo generato in SystemC (se non esistente).

- Verifica del codice sintetizzato con SMV

# 1. Realizzazione modulo IP in VHDL:

- Il modulo IP deve essere descritto a livello RT utilizzando costrutti VHDL sintetizzabili, seguendo gli stili di progettazione presentati a lezione.

- E' consigliato ma non obbligatorio l'uso del tool di design presentato a lezione.

- Il codice generato deve essere opportunamente commentato in inglese.

- Le specifiche del modulo ed eventuali chiarimenti sull'interfaccia di comunicazione da sviluppare sono rilasciati al primo incontro (prenotato possibilmente per email).

#### (EDALab

# 2. Realizzazione testbench per la verifica preliminare:

- Deve essere realizzato un modulo da collegare all'IP per la generazione di stimoli in ingresso.

- Il modulo generato e il modulo IP devono essere istanziati e collegati opportunamente in un modulo top-level.

- L'analisi delle porte d'uscita deve essere realizzato con il tool Modelsim presentato a lezione.

# 3. Sintesi del codice prodotto:

- Il codice prodotto a livello RT deve essere sintetizzato a livello Gate, utilizzando il tool di sintesi Leonardo presentato a lezione.

- Deve essere utilizzata la libreria minc.lib per la sintesi, reperibile in http://profs.sci.univr.it/~bombieri/HDL/SPALab/lib synth/

# 4. Verifica del codice sintetizzato:

Il codice sintetizzato deve essere sottoposto ad una verifica preliminare di correttezza, utilizzando il testbench prodotto a livello RT.

#### (EDALab

# 5. Documentazione:

- L'elaborato deve essere presentato con un documento descrittivo (5 pagine) contenente:

- Schema riassuntivo.

- Descrizione delle funzionalità del modulo implementato.

- Caratteristiche dell'interfaccia usata (nome e tipo porte I/O, eventuale throughput, etc.).

- Descrizione e motivazione delle strutture dati, segnali, e tipi adottati (più significativi).

- Problemi riscontrati durante la realizzazione del progetto e soluzioni adottate.

- · Risultati ottenuti.

- Punto extra 1: descrizione del modulo generato in SystemC (se non esistente).

- Lo sviluppo del punto extra deve essere concordato con il docente.

- Il modulo generato in vhdl, deve essere descritto in SystemC

TLM, utilizzando le librerie TLM OSCI fornite dal docente.

- In questo contesto, può essere generato un solo testbench in SystemC ed utilizzato per verificare il modulo IP in SystemC, VHDL RTL e VHDL Gate level.

- Punto extra 2: verifica del codice sintetizzato con smv:

- Il codice sintetizzato può essere verificato formalmente utilizzando il tool smv (McMillan version) esprimendo proprietà CTL, come presentato a lezione.

#### (EDALab

- · Modalità presentazione:

- Deve essere consegnato un file

<nomeprogetto.tar.gz> contenente la seguente struttura:

- docs

- pdf: documenti in pdf;

- src: sorgenti documentazione (tex, doc, etc);

- · software

- src: file sorgenti (.vhd, etc.)

- work: eventuali file per la compilazione (Makefile, etc.)

- <nometool>: file generati per o prodotti dal tool usato (.do, minc.lib, etc).

- · Elenco elaborati:

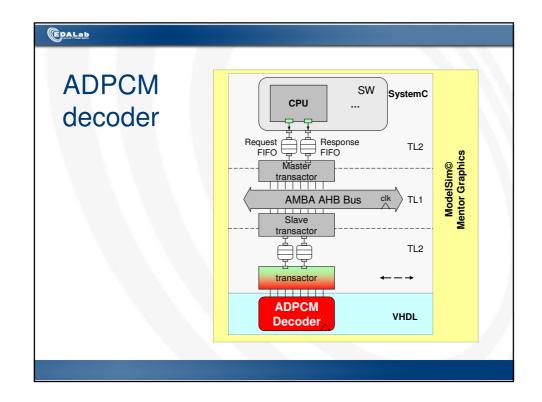

- Decoder ADPCM (1 gruppo + 1 gruppo)

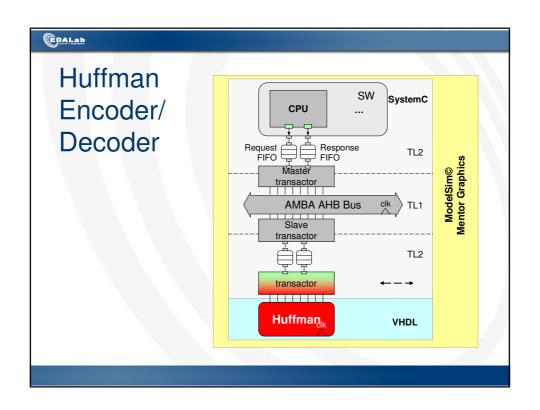

- Encoder Huffman (1 gruppo + 1 gruppo)

- Decoder Huffman (1 gruppo + 1 gruppo)

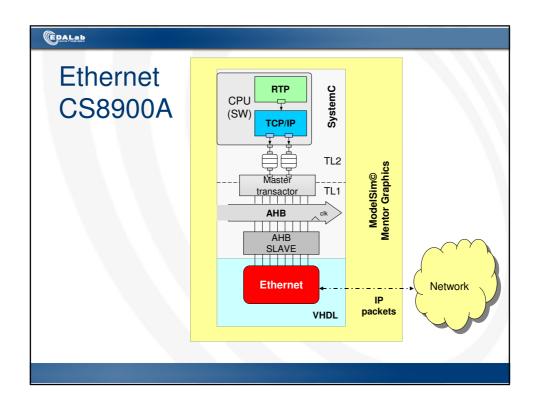

- Ethenret CS8900A (2 gruppi + 2 gruppi)

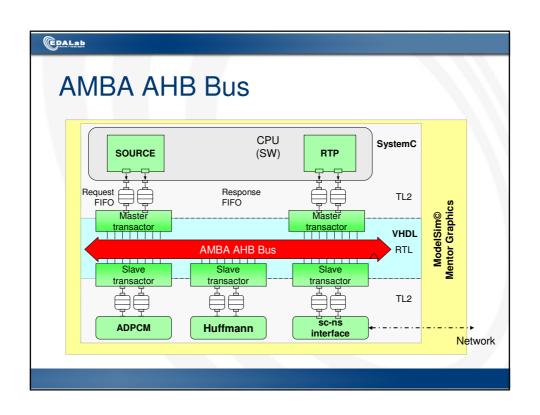

- AMBA AHB Bus (2 gruppi + 2 gruppi)

- Una descrizione sommaria dei moduli e del contesto di applicazione è presentata nelle seguenti slide.